# SOM-TL2837xF

核心板规格书

## 广州创龙电子科技有限公司

© 2013 Guangzhou Tronlong Electronic Technology Co.,Ltd.

#### **Revision History**

| _     | Draft Date | Revision No. | Description    |

|-------|------------|--------------|----------------|

| - EST | 13-        |              | 1. 更新核心板图片。    |

|       | 2022/09/06 | V1.1         | 2. 更新核心板机械尺寸图。 |

|       |            |              | 3. 内容描述优化与勘误。  |

|       | 2022/06/28 | V1.0         | 1. 初始版本。       |

### 目 录

| 1 核心板简介  | 4  |

|----------|----|

| 2 典型应用领域 | 5  |

| 3 软硬件参数  | 5  |

| 4 开发资料   | 10 |

| 5 电气特性   | 10 |

| 6 机械尺寸   | 11 |

| 7 产品订购型号 | 12 |

| 8 技术服务   | 13 |

| 9 增值服务   | 13 |

| 更多帮助     | 14 |

|          |    |

|          |    |

### 1核心板简介

创龙科技 SOM-TL2837xF 是一款基于 TI C2000 系列 TMS320F2837xD 双核 C28x 32 位 浮点 DSP + 紫光同创 Logos/Xilinx Spartan-6 FPGA 处理器设计的工业级核心板。核心板板载 SPI NOR FLASH 和 SRAM 存储器,内部 TMS320F2837xD 与 Logos/Spartan-6 通过 EMI F、uPP、I2C 通信总线连接,通过工业级 B2B 连接器引出 EMIF、ePWM、eQEP、eCAP、C AN、USB 等接口。核心板经过专业的 PCB Layout 和高低温测试验证,稳定可靠,可满足各种工业应用环境。

用户使用核心板进行二次开发时,仅需专注上层运用,降低了开发难度和时间成本,可快速进行产品方案评估与技术预研。

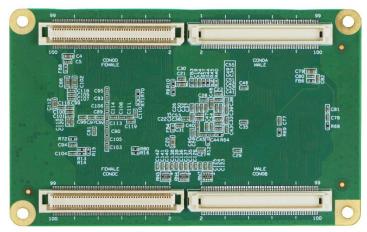

图 1 核心板正面图

图 2 核心板背面图

图 3 核心板斜视图

图 4 核心板侧视图

## 2 典型应用领域

- ✓ 多电平变流器

- ✓ 有源电力滤波器

- ✓ 无功补偿装置

- ✔ 开关电源设备

- ✔ 电机驱动器

- ✓ 飞行控制器

### 3 软硬件参数

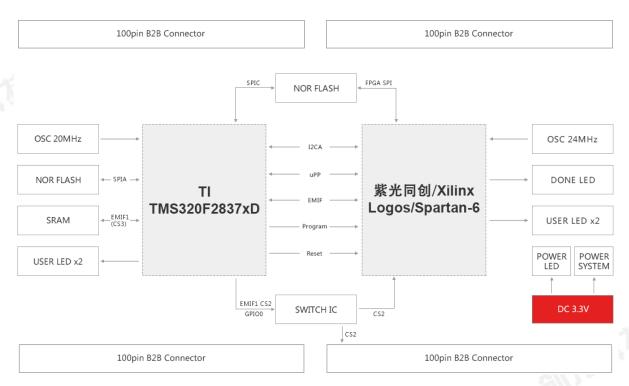

硬件框图

图 5 核心板硬件框图

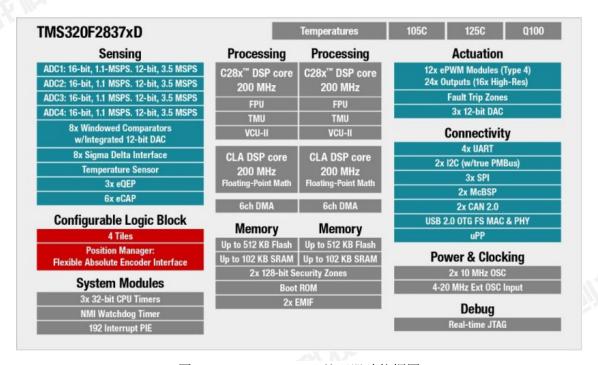

图 6 TI TMS320F2837xD 处理器功能框图

公司官网: www.tronlong.com 技术论坛: www.51ele.net 销售邮箱: sales@tronlong.com 技术邮箱: support@tronlong.com

公司总机: 020-8998-6280 技术热线: 020-3893-9734

|        | 器件         | 型号                  | PGL12G   | PGL22G             | PGL22GS  | PGL25G    | PGL50G    | PGL50H    | PGL100H   |

|--------|------------|---------------------|----------|--------------------|----------|-----------|-----------|-----------|-----------|

| 逻辑资源   | 等效 LUT4    |                     | 12480    | 21043              | 21043    | 27072     | 51360     | 51360     | 102451    |

| 245/// | Flip-Flops | (个)                 | 15600    | 26304              | 26304    | 33840     | 64200     | 64200     | 128064    |

|        | 分布式 RAM    | /(Kbit)             | 84       | 71                 | 71       | 242       | 544       | 544       | 993       |

| RAM 资源 | 块 RAM 数    | 量(18Kbit/块)         | 30       | 48                 | 48       | 60        | 134       | 134       | 286       |

|        | 块 RAM(Kb   | it)                 | 540      | 864                | 864      | 1080      | 2412      | 2412      | 5148      |

| 时钟资源   | PLL        |                     | 4        | 6                  | 6        | 4         | 5         | 5         | 8         |

|        | 最大用户IC     | )                   | 160      | 240                | 140      | 308       | 341       | 304       | 498       |

| IO 资源  | 最大差分IC     | )(对)                | 80       | 120                | 68       | 154       | 170       | 152       | 249       |

|        | DDR3 (Mb   | ps)                 | 800      | 800#               | 800      | 800       | 800       | 800       | 800       |

| -      | APM(18*18  | )                   | 20       | 30                 | 30       | 40        | 84        | 84        | 188       |

|        | ADC 硬核     |                     | 1        | 1                  | -        | _         | -:        | -         | _         |

| 硬核资源   | PCIe Gen2  | x4                  | _        | _                  | _        |           | _         | 1         | 1         |

|        | AES 模块     |                     | 1        | 1                  | 1        | =         | 1         | 1         | 1         |

|        | HSST(6.37  | 5Gbps)              | _        | _                  | _        | _         | _         | 4         | 8         |

| 封装     | 尺寸(mm)     | 间距(mm)              |          |                    | 用户       | IO/差分对    | /HSST     |           |           |

| LPG144 | 22 x 22    | 0.5                 | 103/51/0 |                    |          |           |           |           |           |

| FBG256 | 17 x 17    | 1.0                 | 160/80/0 | 186/93/0           |          | 186/93/0  |           |           |           |

| MBG324 | 15 x 15    | 0.8                 |          | 240/120/0          |          | 226/113/0 | 218/109/0 |           |           |

| LPG176 | 22 x 22    | 0.4                 |          |                    | 140/68/0 |           |           |           |           |

| FBG484 | 23 x 23    | 1.0                 |          |                    |          | 308/154/0 | 332/170/0 | 296/148/4 |           |

| FBG900 | 31 x 31    | 1.0                 |          |                    |          |           |           |           | 498/249/8 |

| 备注: 1  | 、"*"标为在研署  | 条件; 2、"#" <b></b> 标 |          | DDR3 硬核<br>图 7 Log | os 特性    |           |           |           |           |

备注: 1、"\*"标为在研器件; 2、"#"标为该器件支持 DDR3 硬核

#### 图 7 Logos 特性

| Device Logic Cells <sup>(1)</sup> |                               | Configurable Logic Blocks (CLBs) |            |                                |                                  | Block RAM Blocks     |          | Memory              | Endpoint                                     | Maximum                   | Total | Max          |             |

|-----------------------------------|-------------------------------|----------------------------------|------------|--------------------------------|----------------------------------|----------------------|----------|---------------------|----------------------------------------------|---------------------------|-------|--------------|-------------|

|                                   | Logic<br>Cells <sup>(1)</sup> | Slices <sup>(2)</sup>            | Flip-Flops | Max<br>Distributed<br>RAM (Kb) | DSP48A1<br>Slices <sup>(3)</sup> | 18 Kb <sup>(4)</sup> | Max (Kb) | CMTs <sup>(5)</sup> | Controller<br>Blocks<br>(Max) <sup>(6)</sup> | Blocks for<br>PCI Express | GTP   | I/O<br>Banks | User<br>I/O |

| XC6SLX4                           | 3,840                         | 600                              | 4,800      | 75                             | 8                                | 12                   | 216      | 2                   | 0                                            | 0                         | 0     | 4            | 132         |

| XC6SLX9                           | 9,152                         | 1,430                            | 11,440     | 90                             | 16                               | 32                   | 576      | 2                   | 2                                            | 0                         | 0     | 4            | 200         |

| XC6SLX16                          | 14,579                        | 2,278                            | 18,224     | 136                            | 32                               | 32                   | 576      | 2                   | 2                                            | 0                         | 0     | 4            | 232         |

| XC6SLX25                          | 24,051                        | 3,758                            | 30,064     | 229                            | 38                               | 52                   | 936      | 2                   | 2                                            | 0                         | 0     | 4            | 266         |

| XC6SLX45                          | 43,661                        | 6,822                            | 54,576     | 401                            | 58                               | 116                  | 2,088    | 4                   | 2                                            | 0                         | 0     | 4            | 358         |

图 8 Spartan-6 特性

#### 硬件参数

#### 表 1 DSP 端硬件参数

|     | 7. 74.2.11.2.22                                          |

|-----|----------------------------------------------------------|

|     | TI C2000 TMS320F28377D/TMS320F28379D                     |

| 悦   | 2x C28x Core,主频 200MHz                                   |

| DSP | 2x CLAs(Programmable Control Law Accelerators),主频 200MHz |

|     | 1x CLB(Configurable Logic Block),4 tiles,可用软件实现自定义数字逻辑功能 |

|     | (Only TMS320F28379D)                                     |

## 因我们的存在,让嵌入式应用更简单

公司官网: www.tronlong.com 技术论坛: www.51ele.net

销售邮箱: sales@tronlong.com 技术邮箱: support@tronlong.com

公司总机: 020-8998-6280 技术热线: 020-3893-9734

|               | 512KByte FLASH Per Core,片内                                                                                                                                                                                                                                                                                                                                                                      |       |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| ROM           | 32Mbit SPI NOR FLASH,片外                                                                                                                                                                                                                                                                                                                                                                         | 1     |

| 3-            | 204KByte,片内                                                                                                                                                                                                                                                                                                                                                                                     |       |

| RAM           | 512KByte SRAM,片外                                                                                                                                                                                                                                                                                                                                                                                | SILLE |

| B2B Connector | 2x 100pin 公座 B2B 连接器,2x 100pin 母座 B2B 连接器,间距 0.6mm,合高 4.0mm,共 400pin                                                                                                                                                                                                                                                                                                                            |       |

| 150           | 1x 电源指示灯                                                                                                                                                                                                                                                                                                                                                                                        |       |

| LED           | 2x 用户可编程指示灯                                                                                                                                                                                                                                                                                                                                                                                     |       |

| 在間接           | 2x EMIF(EMIF1、EMIF2), 16/32bit 数据线 EMIF1 支持 4 个片选信号(EM1CS0n、EM1CS2n、EM1CS3n、EM1CS4n) EMIF2 支持 2 个片选信号(EM2CS0n、EM1CS2n) 备注: 在核心板内部,EMIF1(EM1CS2n,16bit)已连接至 FPGA 端 IO,EM1CS2n 片选通过选择器(软件使能)引出至 B2B 连接器;在核心板内部,EMIF1(EM1CS3n,16bit)已连接至 DSP 端 SRAM,EM1CS3n 片选未引出至 B2B 连接器; EM1CS0n 片选已引出至 B2B 连接器,但与 I2C 功能复用; EM1CS4n 片选已引出至 B2B 连接器,但与 SCI 功能复用; EM2CS0n、EM1CS2n 片选未引出至 B2B 连接器,用作核心板 LED 控制引脚; | 13-   |

|               | 1x USB 2.0  1x uPP,8bit 数据线                                                                                                                                                                                                                                                                                                                                                                     | -     |

| <b>海</b>      | 备注: 在核心板内部, uPP 总线已连接至 FPGA 端 IO, 未引出至 B2B 连接器; 24x ePWM                                                                                                                                                                                                                                                                                                                                        | -     |

| 硬件资源          | 16x HRPWM                                                                                                                                                                                                                                                                                                                                                                                       | _     |

|               | 6x eCAP                                                                                                                                                                                                                                                                                                                                                                                         | -     |

|               | 3x eQEP                                                                                                                                                                                                                                                                                                                                                                                         | ~ 17. |

|               | 8x SDFM                                                                                                                                                                                                                                                                                                                                                                                         | L III |

|               | 4x ADC,支持 16bit 模式(共 12 路差分输入,1.1MSPS)或 12bit 模式(共 24 路单端输入,3.5MSPS)                                                                                                                                                                                                                                                                                                                            |       |

|               | 3x DAC,12bit                                                                                                                                                                                                                                                                                                                                                                                    |       |

| 勞             | 2x CAN                                                                                                                                                                                                                                                                                                                                                                                          | 1     |

|               | 2x McBSP                                                                                                                                                                                                                                                                                                                                                                                        | 1     |

|               | 4x SCI                                                                                                                                                                                                                                                                                                                                                                                          | 1     |

| L             | 1                                                                                                                                                                                                                                                                                                                                                                                               | J     |

## 因我们的存在,让嵌入式应用更简单

公司官网: www.tronlong.com 技术论坛: www.51ele.net 销售邮箱: sales@tronlong.com 技术邮箱: support@tronlong.com 公司总机: 020-8998-6280 技术热线: 020-3893-9734

2x I2C(I2CA、I2CB)

备注: 在核心板内部, I2CA 总线已连接至 FPGA 端 IO, 同时引出至 B2B 连接器;

3x SPI(SPIA、SPIB、SPIC)

备注:

在核心板内部,SPIA 总线已连接至 DSP 端 SPI NOR FLASH,同时引出至 B2B 连接器:

在核心板内部,SPIC 总线已连接至 FPGA 端 SPI NOR FLASH(实现通过 DSP 端烧写 FPGA 端 SPI NOR FLASH 功能),同时引出至 B2B 连接器;

SPIB 已引出至 B2B 连接器;

备注: B2B、电源、指示灯等部分硬件资源, DSP 与 FPGA 共用。

#### 表 2 FPGA 端硬件参数

|                      |                                      | •                                  |  |  |

|----------------------|--------------------------------------|------------------------------------|--|--|

| FPGA                 | 紫光同创 Logos PGL25G-6IMBG324           | Xilinx Spartan-6 XC6SLX16-2CSG324I |  |  |

| ROM                  | 64Mbit SPI NOR FLASH                 | · les                              |  |  |

| 150                  | 1x DONE 指示灯                          | all TE III                         |  |  |

| LED                  | 2x 用户可编程指示灯                          | 12.3                               |  |  |

| Logic Cells(LUT4)    | 27072                                | 14579                              |  |  |

| Flip-Flops           | 33840                                | 18224                              |  |  |

| DSP Slice            | 40(APM,Arithmetic Process Module)    | 32                                 |  |  |

| Block<br>RAM(18Kbit) | 60                                   | 32                                 |  |  |

| СМТ                  | 4(PLL)                               | 2                                  |  |  |

| 10                   | 单端 (24 个), 差分对 (69 对), 共<br>162 个 IO | 单端(30个),差分对(69对),共168<br>个IO       |  |  |

#### 软件参数

#### 表 3

| DSP 端软件支持 | 裸机(C2000Ware)、SYS/BIOS                      |

|-----------|---------------------------------------------|

| ccs 版本号   | CCS7.4.0                                    |

| 软件开发套件提供  | C2000Ware_1_00_06_00,bios_6_52_00_12        |

| PDS 版本号   | Pango Design Suite 2021.1-SP7.1(紫光同创 Logos) |

| ISE 版本号   | ISE 14.7(Xilinx Spartan-6)                  |

## 因我们的存在,让嵌入式应用更简单

公司官网: www.tronlong.com 技术论坛: www.51ele.net 销售邮箱: sales@tronlong.com 技术邮箱: support@tronlong.com 公司总机: 020-8998-6280 技术热线: 020-3893-9734

### 4 开发资料

- (1) 提供核心板引脚定义、可编辑底板原理图、可编辑底板 PCB、芯片 Datasheet,缩短硬件设计周期:

- (2) 提供丰富的 Demo 程序;

- (3) 提供完整的平台开发包、入门教程,节省软件整理时间,让应用开发更简单;

- (4) 提供详细的 DSP + FPGA 通信开发案例,完美解决 DSP + FPGA 通信开发瓶颈。 DSP 端开发案例主要包括:

- ▶ 裸机(C2000Ware)开发案例

- ➤ RTOS(SYS/BIOS)开发案例

- > 双核通信开发案例

- ➤ CLA 算法开发案例

- ➤ AD、DA 开发案例

- ▶ ePWM、eCAP、eQEP 开发案例

- ➤ EMIF 网口开发案例

DSP + FPGA 开发案例主要包括:

- ▶ 基于 I2C 的通信案例

- ▶ 基于 EMIF 的通信案例

- ▶ 基于 uPP 的多通道 AD 采集传输处理综合案例

### 5 电气特性

工作环境

表 4

| 环境参数 | 最小值 | 典型值 | 最大值 |

|------|-----|-----|-----|

|------|-----|-----|-----|

### 因我们的存在,让嵌入式应用更简单

公司官网: www.tronlong.com 技术论坛: www.51ele.net 销售邮箱: sales@tronlong.com 技术邮箱: support@tronlong.com 公司总机: 020-8998-6280 技术热线: 020-3893-9734

| 工作温度 | -40°C | /    | 85°C |

|------|-------|------|------|

| 工作电压 | /     | 3.3V | /    |

#### 功耗测试

|      | 表     | 5     |       |

|------|-------|-------|-------|

| 工作状态 | 电压典型值 | 电流典型值 | 功耗典型值 |

| 状态 1 | 3.3V  | 0.17A | 0.56W |

| 状态 2 | 3.3V  | 0.22A | 0.73W |

备注: 功耗基于 TL2837xF-EVM 评估板测得。测试数据与具体应用场景有关,仅供参考。

状态 1: 评估板不接入外接模块,DSP 运行 LED 测试程序,FPGA 运行 LED 测试程序。

状态 2: 评估板不接入外接模块, DSP 运行 FFT 测试程序, 2 个 C28x 核心的资源使用率约为 100%; F PGA 运行 DRAM 测试程序, 电源估算功率为 0.022W。

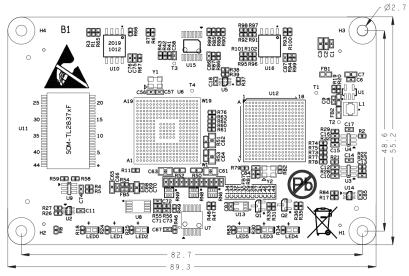

### 6 机械尺寸

| PCB 尺寸 | 55.2mm*89.3mm |       |

|--------|---------------|-------|

| PCB 层数 | 8 层           |       |

| PCB 板厚 | 1.6mm         |       |

| 安装孔数量  | 4 个           | 到美    |

|        |               | LE MA |

图 9 核心板机械尺寸图

## 7 产品订购型号

表 7

| 型号                    | DSP/FPGA       | DSP 主频 | SRAM     | SPI NOR FLASH<br>(DSP/FPGA) | 温度<br>级别 |

|-----------------------|----------------|--------|----------|-----------------------------|----------|

| SOM-TL28377DF-200/25  | TMS320F28377D/ | 200MHz | 512KByte | 32Mbit/64Mbit               | 工业级      |

| G-32MN4MD-I-B1        | PGL25G         |        |          |                             | ±±20     |

| SOM-TL28379DF-200/25  | TMS320F28379D/ | 200MHz | 512KByte | 32Mbit/64Mbit               | 工业级      |

| G-32MN4MD-I-B1        | PGL25G         |        |          |                             | 工业级      |

| SOM-TL28377DF-200/16- | TMS320F28377D/ | 200MHz | 512KByte | 32Mbit/64Mbit               | 工业级      |

| 32MN4MD-I-B1          | XC6SLX16       |        |          |                             | 工业级      |

| SOM-TL28379DF-200/16- | TMS320F28379D/ | 200MHz | 512KByte | 32Mbit/64Mbit               | 工业级      |

| 32MN4MD-I-B1          | XC6SLX16       |        |          |                             | 工业级      |

备注: 标配为 SOM-TL28377DF-200/25G-32MN4MD-I-B1, 其他型号请与相关销售人员联系。

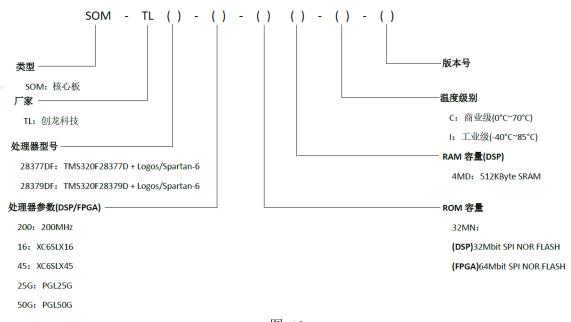

#### 型号参数解释

#### 图 10

### 8 技术服务

- (1) 协助底板设计和测试,减少硬件设计失误;

- (2) 协助解决按照用户手册操作出现的异常问题;

- (3) 协助产品故障判定:

- (4) 协助进行产品二次开发;

- (5) 提供长期的售后服务。

### 9 增值服务

- 主板定制设计

- 核心板定制设计

- 嵌入式软件开发

- 项目合作开发

- 技术培训

### 更多帮助

销售邮箱: sales@tronlong.com

技术邮箱: support@tronlong.com

创龙总机: 020-8998-6280

技术热线: 020-3893-9734

创龙官网: www.tronlong.com

技术论坛: www.51ele.net

官方商城: https://tronlong.tmall.com

TMS320F2837x 交流群: 475426667、486354767

TI 中文论坛: www.deyisupport.com

TI 英文论坛: http://e2e.ti.com

TI 官网: www.ti.com

Logos、Spartan-6 交流群: 311416997、101245165

紫光同创官网: www.pangomicro.com

Xilinx 官网: www.xilinx.com

Xilinx 论坛: https://forums.xilinx.com

Xilinx WIKI: https://xilinx-wiki.atlassian.net/wiki/spaces/A/overview